# MIDDLE EAST TECHNICAL UNIVERSITY

# ELECTRICAL AND ELECTRONICS ENGINEERING DEPARTMENT

EE446

Computer Architecture II

# Laboratory Manual

Course Instructors: Prof. Dr. Ece Güran Schmidt Laboratory Assistants: Doğu Erkan Arkadaş Barış Tiryakı

March 2023

# Contents

| 1        | Laboratory Regulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | 1.1 Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 |

|          | 1.2 Cheating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|          | 1.3 Remarks and Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| <b>2</b> | General Information about Laboratory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 |

|          | 2.1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 |

| 3        | Quartus Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6 |

| 4        | Simulation Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7 |

|          | 4.1 Simulation using cocotb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7 |

| <b>5</b> | Some Useful How-to Items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 |

|          | 5.1 How to create a Verilog module with parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8 |

|          | 5.2 How to initialize the Memory on FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

|          | 5.3 Problems with running Cocotb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9 |

|          | 5.3.1 Path Issues 5.1 Path Issue 5.1 Path Iss | 9 |

|          | 5.3.2 "I give up" error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|          | 5.4 Making your Code Compile Faster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|          | 5.4.1 Avoiding Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

#### **Course Instructors**

Namee-mailRoomProf. Dr. Ece Güran Schmidteguran@metu.edu.trA-402

# Laboratory Assistants

| Name               | e-mail               | Room  |

|--------------------|----------------------|-------|

| Doğu Erkan Arkadaş | arkadas@metu.edu.tr  | A-404 |

| Barış Tiryaki      | btiryaki@metu.edu.tr | A-405 |

#### **1** Laboratory Regulations

This laboratory is a very important part of EE446 - Computer Architecture II course to understand the concepts in the computer architecture lectures thoroughly. By attending experiments and completing all the work, the key concepts and most of the abstract parts of the lectures can be grasped very easily. Thus, it is important to know the regulating rules of this laboratory for both a better understanding and for your grades.

There are rules for the regulation of EE446 Laboratory. These rules are strict, and by taking EE446 - Computer Architecture II course, you will be considered that you have understood and accepted all the rules stated below.

#### 1.1 Rules

The rules for EE446 - Computer Architecture II Laboratory are given below. Please read thoroughly:

- 1. The manual of an experiment will be available at least a week before the corresponding experiment.

- 2. A preliminary work to be detailed in each experiment manual has to be prepared for each experiment.

- 3. The preliminary works will be collected last Sunday before the corresponding laboratory week through the ODTUCLASS.

- 4. Preliminary work is a crucial part of the laboratory work in preparing for the experiment and understanding the concepts to be covered in the corresponding experiment. Thus, You will NOT be allowed to <u>attend</u> the relevant laboratory session without any preliminary work. Partially done preliminary work reports are acceptable if at least you got a passing grade of 50%

- 5. Cheating and plagiarism will result in zero grades, whereas disciplinary actions may also be taken. Please read the subsection 1.2 for detailed information about cheating.

- 6. Experiments are to be performed individually.

- 7. Grading for each laboratory work will be 40% preliminary work and 60% laboratory performance.

- 8. Talking and sharing information between students during a laboratory session is strictly forbidden. Repeated offenses of this rule will make your lab performance grade 0.

- 9. No extra time will be given to the latecomers.

- 10. To leave the laboratory room during a session, you must get permission from the laboratory assistant.

- 11. Transfer between laboratory sessions (e.g. from *Group 1* to *Group 5*) will NOT be allowed unless you have a valid excuse (medical report, etc.).

- 12. Your codes have to be well commented. The codes lacking any comments or overly laden with comments will not be evaluated. Please read the subsection 1.3 for detailed information about coding and commenting.

- 13. Students with officially documented legal excuses will be allowed to take make-ups. Only academic permissions (given by the University), signed confirmation from the instructors for any exam clashes, and METU Health and Counseling Center (MEDIKO) will be considered valid documents for the right to take make-ups. You may take at most three make-ups even if you have more than three officially documented legal excuses.

#### Since preliminary work spans several weeks unless you have a valid excuse for the said weeks, you will not be allowed to submit new preliminary work

14. Students who do not attend or get zero grades from **3 or more** experiments, excluding the first one, will get N/A from the EE446 course. These students also won't be allowed to participate in the term project. Please note that insufficient preparation of the preliminary work of an experiment or plagiarism is equivalent to not attending the corresponding experiment.

- 15. Be gentle with the FPGAs as they are expensive. Each FPGA costs around 364£ before shipping and tax. You will lose performance grades if you handle FPGAs roughly during the laboratory sessions or do not put them in their boxes properly at the end of the sessions.

- 16. Bringing materials outside of those provided to the laboratory (written codes, etc.) are strictly prohibited

#### 1.2 Cheating

You are considered to graduate and become an engineer in 1 or 2 years. Hence, you are expected to act according to the professionalism required as a METU graduate.

Copying work from any other resource (web page, your friend's report, older resources you have found, etc.) during preliminary work or sharing information or code files during sessions is considered cheating. Automated tools such as ChatGPT are allowed if the output is changed sufficiently to be different from other students; otherwise, it will count as plagiarism.

Helping your friends, studying together, or any form of cooperation is encouraged -since it fosters your relationships with others and helps you learn the topic better- but YOU do your own work. Creating only one report/code is not studying together or is not cooperation and will NOT be accepted.

#### 1.3 Remarks and Evaluation

Your laboratory grade comprises your preliminary work grade and laboratory session performance grade. Preliminary work requires the implementation of different computer architectures, all of which are used to experiment during the laboratory sessions. The performance grade is based on the functionality of your implementations, the comprehensiveness of your knowledge of the related laboratory topic, and how much help you get from your TAs. TAs will help you as if they are your laboratory partner; however, any big help you receive (such as a TA writing code for you or fixing major issues in your design) will result in a percentage reduction in your laboratory performance grade. If a big part of the design is not implemented in your preliminary work, you will most likely get ZERO performance grades from the corresponding step, as implementing the design during the laboratory session is nearly impossible.

Implementations without comments will not be considered valid implementations of the tasks, and the corresponding task will not be evaluated. You are expected to write down explanatory comments in your code. That does not mean you should write an explanation next to each code line. What is required is an explanation of the functionality of the code blocks and the functionality of the representative code lines where necessary.

You are always expected to do proper test benching of your code in software before embedding it into an FPGA. For this laboratory, test benches of all the designs (except for the first laboratory and the term project) will be given to you. You are also expected to practice your implementations with the FPGAs before attending your laboratory session so that major bugs that may cost too much time to fix can be eliminated and you are on the safer side to complete the experimental work within the required time slot. You can practice and work on your implementations by using the laboratory at EA-407, which is open to access 24/7.

#### 2 General Information about Laboratory

As it is mentioned before, this laboratory is a very important part of EE446 - Computer Architecture II course. The laboratory work helps you understand most of the concepts given in the computer architecture lectures.

The experiments will be carried out in Microprocessor Laboratory at EA-409 which is located on the 4th floor of A Block of our department. EA-407 laboratory will be open to access on the weekdays during working hours (09:00-17:00) for you to practice. Hence, you may test and debug your preliminary work prior to your laboratory session.

Figure 1: Microprocessor and Computer Architecture Laboratory, A Building, Room 407

There are different sessions of laboratory and you are assigned to one of the sessions to perform your experiments.

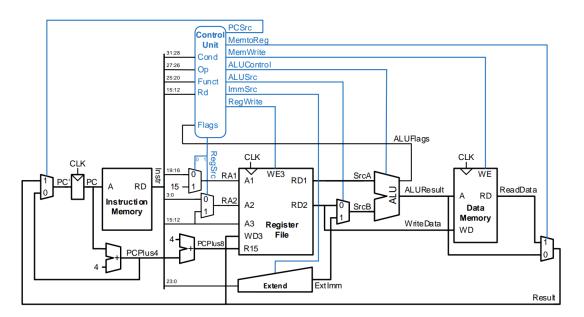

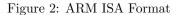

There will be a total of 4 experiments and 1 course project. These experiments and the project are based on constructively practicing the design of computers via Verilog hardware description language and will be on the following subjects:

- Fundamental modules for computer design

- Single cycle computer

- Multi-cycle computer

- Pipelined computer

- Project: Simplified RISC-V Computer

#### 2.1 Experimental Setup

The experimental setup of EE446 Laboratory is composed of the following items:

- A notebook computer

- You may login as a student, which does not require any password

- Computer has Quartus and other materials you may need during the lab/ when practicing

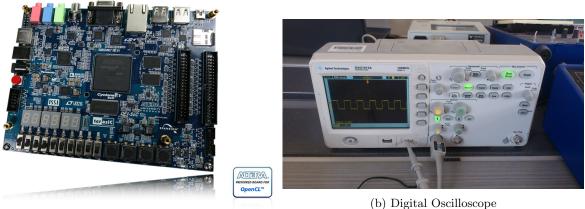

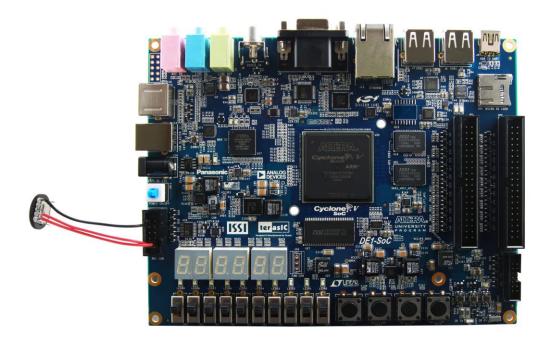

- DE1-SoC Development Kit A board containing Altera Cyclone V 5CSEMA5F31C6N FPGA

- DE1-SoC is connected to the notebook via a USB data cable.

- DE1-SoC is programmed via Quartus installed on the notebook (to be explained in Section 3).

(a) DE1-SoC Board

- For simulation purposes, cocotb is installed on the notebooks (to be explained in Section 4.1).

- Digital Oscilloscope Oscilloscope for debugging purposes

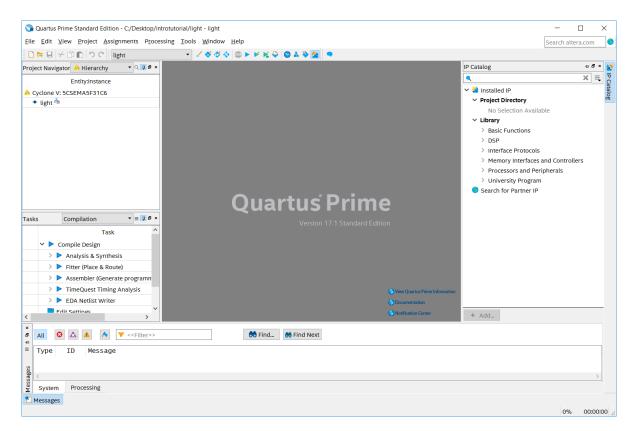

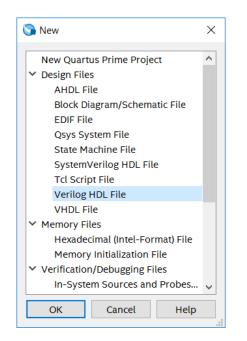

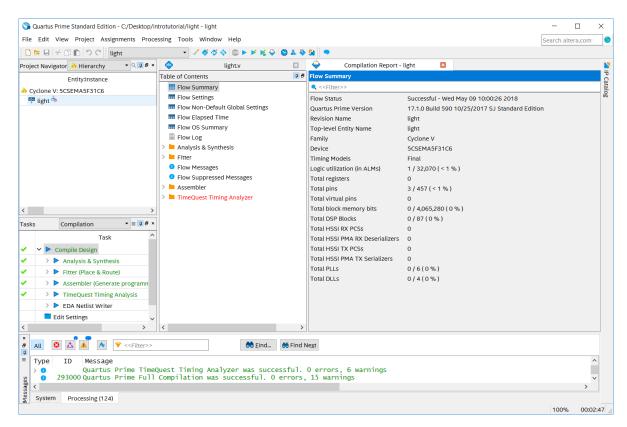

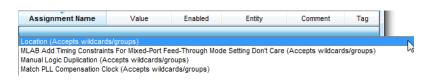

#### 3 Quartus Software

Throughout the labs of this semester, we will be using Quartus Prime Lite Edition to be able to program the DE1-SoC FPGA board. This requires very little know-how in creating a project, adding files, compiling, and programming with the compiled board. To learn how to do this you should read sections 4-6 of Quartus Prime IntroductionUsing Verilog Designs documents. DE1-SOC board pin assignments and project creation will be done using the vendor supplied DE1-SoC System Builder program which you should read about in DE1-SoC user manual l section 4. These are very light readings which should only take about 30 minutes of your time, read them before attending laboratory sessions.

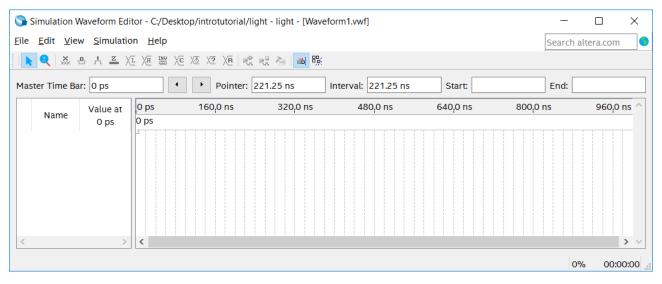

#### 4 Simulation Software

This section introduces simulation software to be used throughout the laboratory work to perform behavioral simulation for the Verilog design codes and embed the designs to the FPGA, respectively. Basics for the cocotb are covered in this section. For more general usage tutorials of the cocotb, one can refer to the tutorials available on the EE446 ODTUClass course page.

#### 4.1 Simulation using cocotb

This part only concisely covers the basics of cocotb. To get a more detailed look into cocotb with installation guides, please check the cocotb document in ODTUCLASS or official cocotb documents.

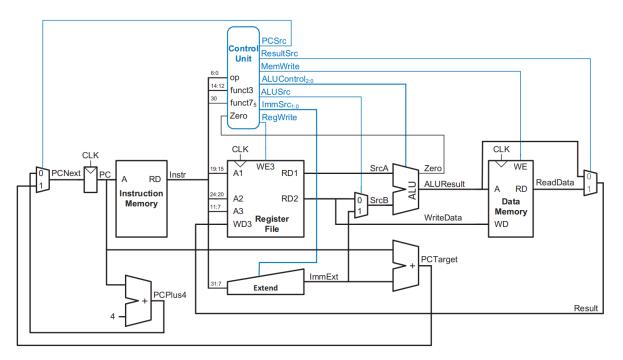

Cocotb is simply an interface between a Verilog simulator (Icarus Verilog for this course) and a Python script you will write (or one that will be given to you) as a test bench. Cocotb will show your Verilog design as an object in the Python script. Thus, every signal in your Verilog design will be a variable of the Verilog object. You can use anything available in Python to verify your design. To better understand this, please check the supplied test bench examples on ODTUCLASS. Since Cocotb is fully on Python, unlike ModelSim, no Verilog knowledge is required to test any design on the bench.

To run your test bench, open the Anaconda Prompt and change the directory to match the location of the test files. If your "User" folder or the folder test-bench is in has a space in its PATH, cocotb will give an error so be mindful of that. Use **make** command to run the test bench with the default simulator (specified in the makefile) or **make sim=icarus** to simulate with Icarus Verilog explicitly.

#### 5 Some Useful How-to Items

In this section, some tips and tricks on using Quartus software and Verilog programming are to be presented. Those can be helpful for your preliminary work tasks.

#### 5.1 How to create a Verilog module with parameters

There are many cases where designing a module should be generalized. For example, a registered design can be used for different data widths. It is cumbersome to implement the same design to support different data widths. To overcome this, some parts of the module can be parametrized so that modules with different properties of the same design can be instantiated. For the register example, one can make the data width a parameter so that by varying the parameter, registers of different data width can be created from the same design.

In Verilog, a module can be easily parameterized. You will just add a parameter block before defining the arguments of the module. An example of a module with parameters is given below:

```

// an example module with parameters

// the module is to split a data bus into two

module bus_split #(parameter W=8, S=4) (bus_in, split_out0, split_out1);

input wire [(W - 1):0] bus_in;

output wire [(W - S - 1):0] split_out1;

output wire [(S - 1):0] split_out0;

assign bus_out0 = bus_in[(S - 1):0];

assign bus_out1 = bus_in[(W - 1):S];

endmodule

```

Note that, the default values of the parameters should be provided so that the module can be instantiated with the default parameters if no parameter setting is performed. To create a module with a specified parameter, the values of the parameters should be supplied to the module in the order they are defined:

```

// assume you want to split the content of the instruction register // say the name of the output of the instruction register is reg_out

```

. . .

```

wire [3:0] instr; // most significant 4 bits are for instruction

wire [11:0] oprnd; // the rest is for operand

bus_split #(16, 12) split_instr(.bus_in(reg_out), .split_out0(oprnd),

.split_out1(instr));

```

. . .

#### 5.2 How to initialize the Memory on FPGA

To initialize the memory on the FPGA you need to use "readmemh" command inside an initial block as in below. One thing you need to make certain of is that the hex file should have elements for each memory location.

For example: If you have a memory with 256 locations each containing a byte hex file should have 256 bytes specified in it.

```

initial begin

$readmemh("instructions.hex", mem, 0);

end

```

#### 5.3 Problems with running Cocotb

#### 5.3.1 Path Issues

Cocotb does not like Turkish characters (as do most software libraries). If you have a Turkish character in your files or in your file path (either the test folder or the folder Icarus/Python is installed) you will get a "Unicode Error" when trying to run tests.

#### 5.3.2 "I give up" error

This is usually because one or more components of your environment are not set up correctly.

The best way to solve this is to go to ODTUClass or the cocotb website and reinstall everything by following the steps. We highly suggest using a version of Anaconda as it handles most of the environment for you.

Also, older Icarus versions can cause this error, so delete the old version and install the latest version (should be v12+).

#### 5.4 Making your Code Compile Faster

#### 5.4.1 Avoiding Latches

For your codes to compile faster, you need to avoid any undesirable latches.

For your combinational circuits to not produce latches, you must specify every signal's value in each possible case.

For example:

If you write a mux like this:

```

always @(*) begin

case(select)

2'b00: output_value = input_0;

2'b01: output_value = input_1;

2'b10: output_value = input_2;

endcase

end

```

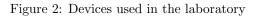

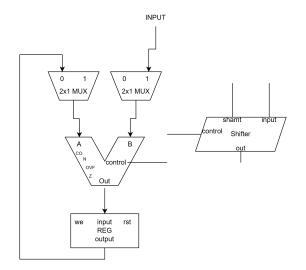

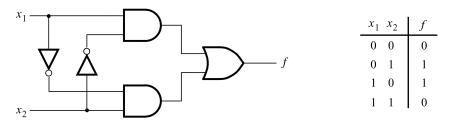

Since 1 case is empty, the synthesizer assumes that case means storing the previous value. A combinational circuit that stores a value results in a latch you can see in Figure 3

The same thing can happen if you have multiple signals in your case statements. Even if some of the signals are "don't care" in some cases, you should always assign a value to every single signal in every case.

Figure 3: Example of a Latch in Synthesis

# DE1-SOC

# USER MANUAL

linn

IIII

Copyright © 2003-2014 Terasic Technologies Inc. All Rights Reserved.

| Chapter 1       | DE1-SoC Development Kit4               |

|-----------------|----------------------------------------|

| 1.1 Package C   | ontents4                               |

| 1.2 DE1-SoC     | System CD                              |

| 1.3 Getting He  | 2lp5                                   |

| Chapter 2       | Introduction of the DE1-SoC Board6     |

| 2.1 Layout and  | l Components                           |

| 2.2 Block Diag  | gram of the DE1-SoC Board              |

| Chapter 3       | Using the DE1-SoC Board 12             |

| 3.1 Settings of | FPGA Configuration Mode                |

| 3.2 Configurat  | ion of Cyclone V SoC FPGA on DE1-SoC13 |

| 3.3 Board Stat  | us Elements                            |

| 3.4 Board Res   | et Elements                            |

| 3.5 Clock Circ  | 21 vuitry                              |

| 3.6 Peripheral  | s Connected to the FPGA23              |

| 3.6.1           | User Push-buttons, Switches and LEDs   |

| 3.6.2           | 7-segment Displays                     |

| 3.6.3           | 2x20 GPIO Expansion Headers            |

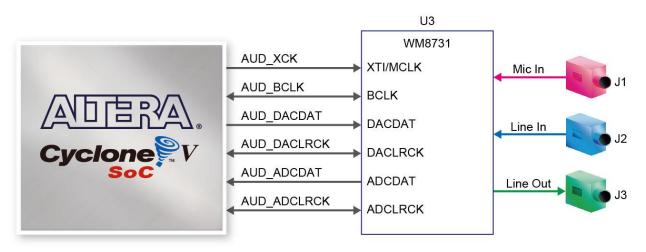

| 3.6.4           | 24-bit Audio CODEC                     |

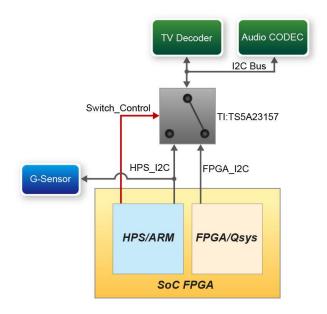

| 3.6.5           | I2C Multiplexer                        |

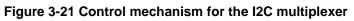

| 3.6.6           | VGA                                    |

| 3.6.7           | TV Decoder                             |

| 3.6.8           | IR Receiver                            |

| 3.6.9           | IR Emitter LED                         |

| 3.6.10                                          | SDRAM Memory                               | 38 |  |  |  |  |  |  |

|-------------------------------------------------|--------------------------------------------|----|--|--|--|--|--|--|

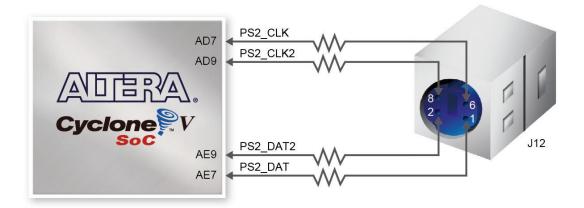

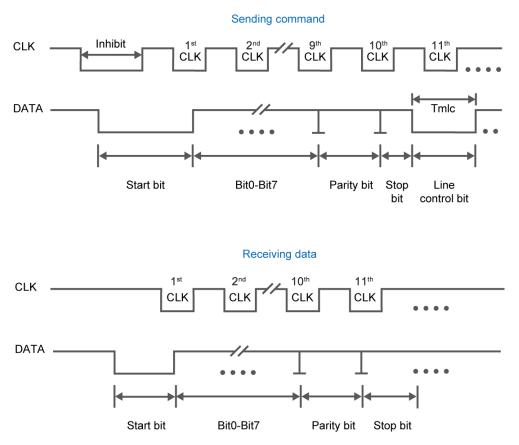

| 3.6.11                                          | PS/2 Serial Port                           |    |  |  |  |  |  |  |

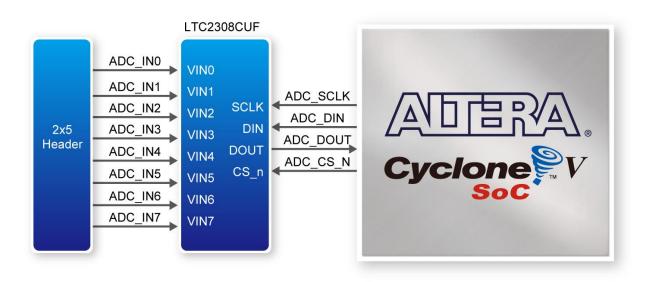

| 3.6.12                                          | A/D Converter and 2x5 Header               | 42 |  |  |  |  |  |  |

| 3.7 Peripheral                                  | s Connected to Hard Processor System (HPS) | 43 |  |  |  |  |  |  |

| 3.7.1                                           | User Push-buttons and LEDs                 | 43 |  |  |  |  |  |  |

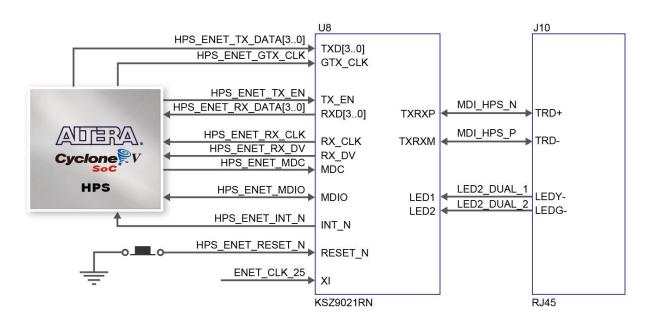

| 3.7.2                                           | Gigabit Ethernet                           | 44 |  |  |  |  |  |  |

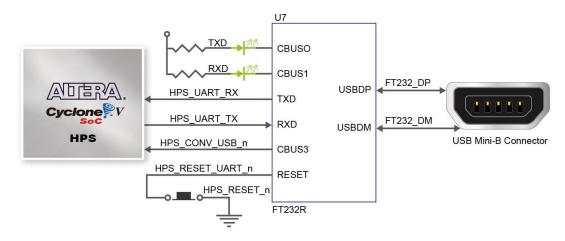

| 3.7.3                                           | UART                                       | 45 |  |  |  |  |  |  |

| 3.7.4                                           | DDR3 Memory                                | 46 |  |  |  |  |  |  |

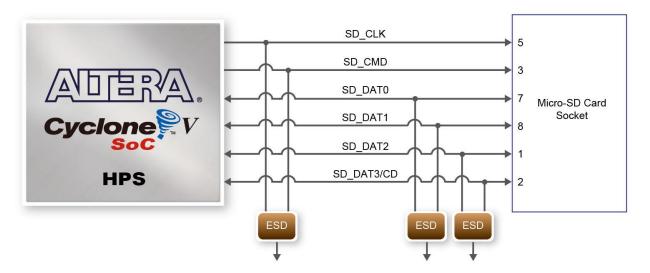

| 3.7.5                                           | Micro SD Card Socket                       | 48 |  |  |  |  |  |  |

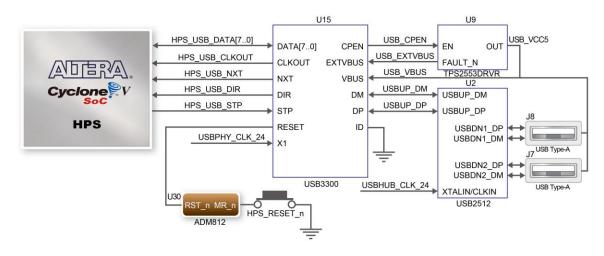

| 3.7.6                                           | 2-port USB Host                            | 49 |  |  |  |  |  |  |

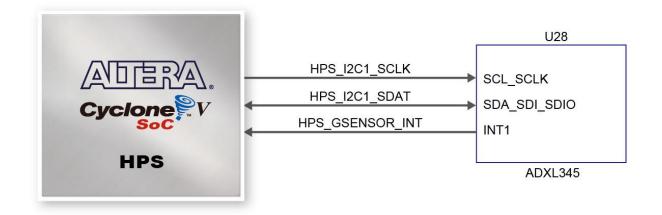

| 3.7.7                                           | G-sensor                                   | 50 |  |  |  |  |  |  |

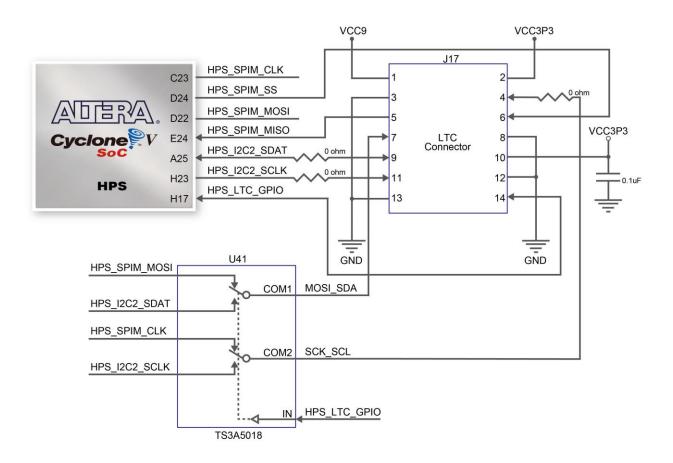

| 3.7.8                                           | LTC Connector                              | 51 |  |  |  |  |  |  |

| Chapter 4                                       | DE1-SoC System Builder                     | 53 |  |  |  |  |  |  |

| 4.1 Introduction                                | on                                         | 53 |  |  |  |  |  |  |

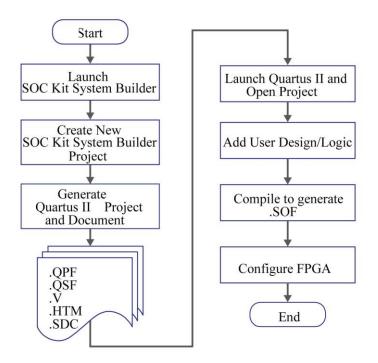

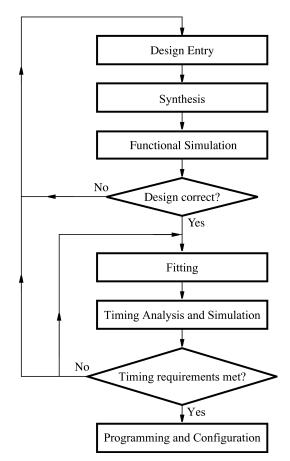

| 4.2 Design Flo                                  | DW                                         | 53 |  |  |  |  |  |  |

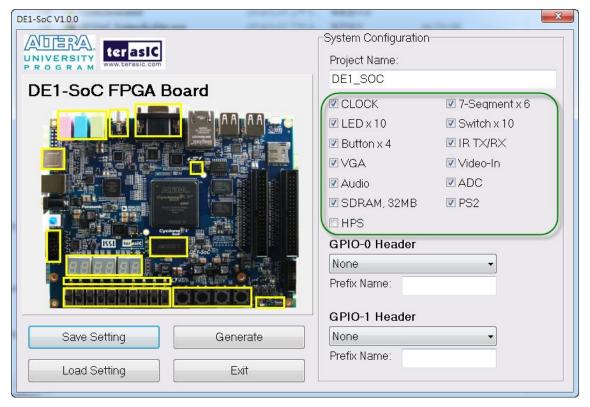

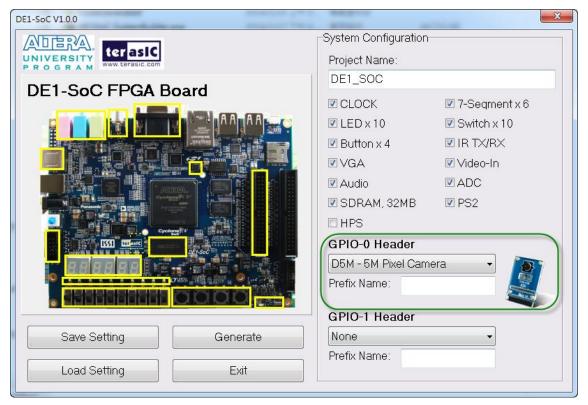

| 4.3 Using DE                                    | 1-SoC System Builder                       | 54 |  |  |  |  |  |  |

| Chapter 5                                       | Examples For FPGA                          | 60 |  |  |  |  |  |  |

| 5.1 DE1-SoC                                     | Factory Configuration                      | 60 |  |  |  |  |  |  |

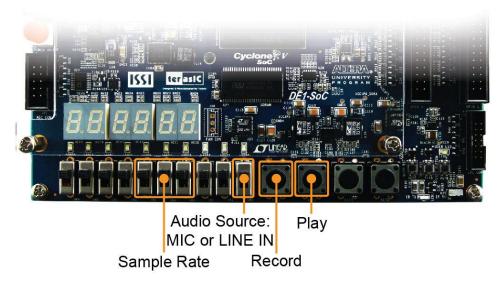

| 5.2 Audio Rec                                   | ording and Playing                         | 61 |  |  |  |  |  |  |

| 5.3 Karaoke N                                   | Iachine                                    | 64 |  |  |  |  |  |  |

| 5.4 SDRAM T                                     | Fest in Nios II                            | 66 |  |  |  |  |  |  |

| 5.5 SDRAM T                                     | Fest in Verilog                            | 69 |  |  |  |  |  |  |

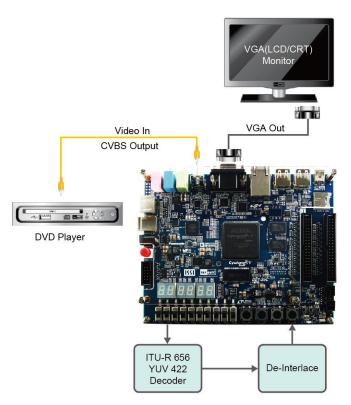

| 5.6 TV Box D                                    | emonstration                               | 71 |  |  |  |  |  |  |

| 5.7 PS/2 Mou                                    | 5.7 PS/2 Mouse Demonstration               |    |  |  |  |  |  |  |

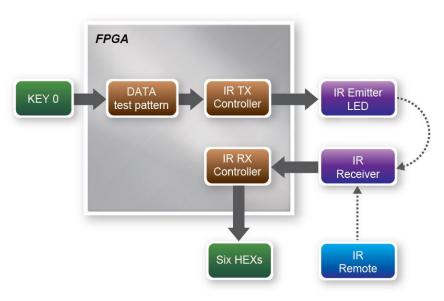

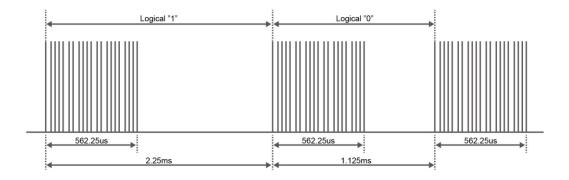

| 5.8 IR Emitter LED and Receiver Demonstration76 |                                            |    |  |  |  |  |  |  |

| 5.9 ADC Read                                    | ling                                       | 82 |  |  |  |  |  |  |

| Chapter 6                                       | Examples for HPS SoC                       | 87 |  |  |  |  |  |  |

| 6.1 Hello Program                                                                                                                                                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2 Users LED and KEY                                                                                                                                                                                     |     |

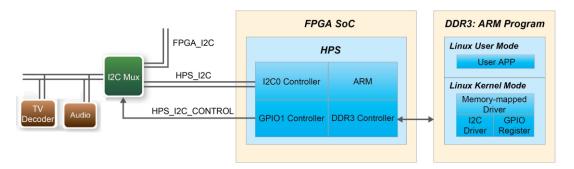

| 6.3 I2C Interfaced G-sensor                                                                                                                                                                               |     |

| 6.4 I2C MUX Test                                                                                                                                                                                          |     |

| Chapter 7 Examples for using both HPS SoC and FGPA                                                                                                                                                        | 101 |

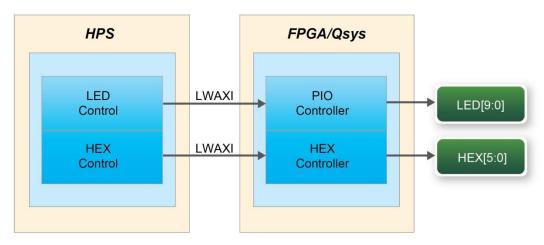

| 7.1 HPS Control LED and HEX                                                                                                                                                                               |     |

| 7.2 DE1-SoC Control Panel                                                                                                                                                                                 |     |

| 7.3 DE1-SoC Linux Frame Buffer Project                                                                                                                                                                    |     |

| Chapter 8 Programming the EPCS Device                                                                                                                                                                     |     |

|                                                                                                                                                                                                           |     |

| 8.1 Before Programming Begins                                                                                                                                                                             |     |

| <ul><li>8.1 Before Programming Begins</li><li>8.2 Convert .SOF File to .JIC File</li></ul>                                                                                                                |     |

|                                                                                                                                                                                                           |     |

| 8.2 Convert .SOF File to .JIC File                                                                                                                                                                        |     |

| <ul><li>8.2 Convert .SOF File to .JIC File</li><li>8.3 Write JIC File into the EPCS Device</li></ul>                                                                                                      |     |

| <ul><li>8.2 Convert .SOF File to .JIC File</li><li>8.3 Write JIC File into the EPCS Device</li><li>8.4 Erase the EPCS Device</li></ul>                                                                    |     |

| <ul> <li>8.2 Convert .SOF File to .JIC File</li> <li>8.3 Write JIC File into the EPCS Device</li> <li>8.4 Erase the EPCS Device</li> <li>8.5 Nios II Boot from EPCS Device in Quartus II v16.0</li> </ul> |     |

# Chapter 1 DE1-SoC Development Kit

The DE1-SoC Development Kit presents a robust hardware design platform built around the Altera System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a high-performance, low-power processor system. Altera's SoC integrates an ARM-based hard processor system (HPS) consisting of processor, peripherals and memory interfaces tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone. The DE1-SoC development board is equipped with high-speed DDR3 memory, video and audio capabilities, Ethernet networking, and much more that promise many exciting applications.

The DE1-SoC Development Kit contains all the tools needed to use the board in conjunction with a computer that runs the Microsoft Windows XP or later.

# **1.1 Package Contents**

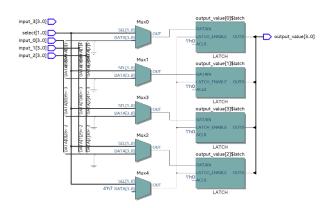

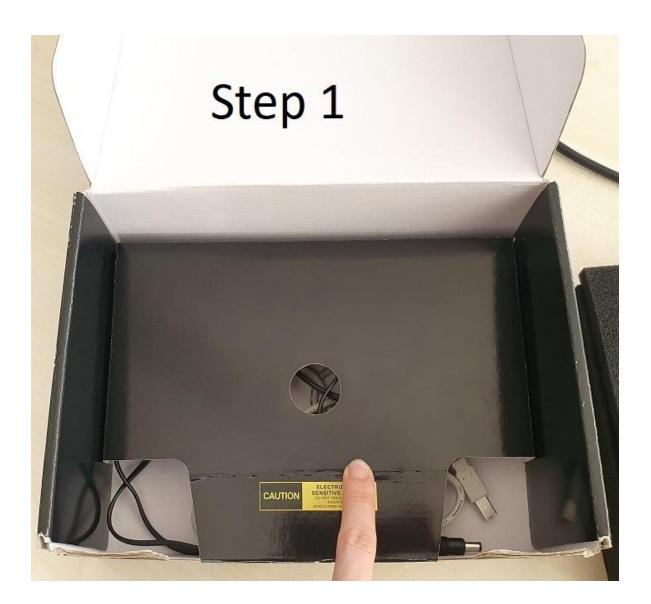

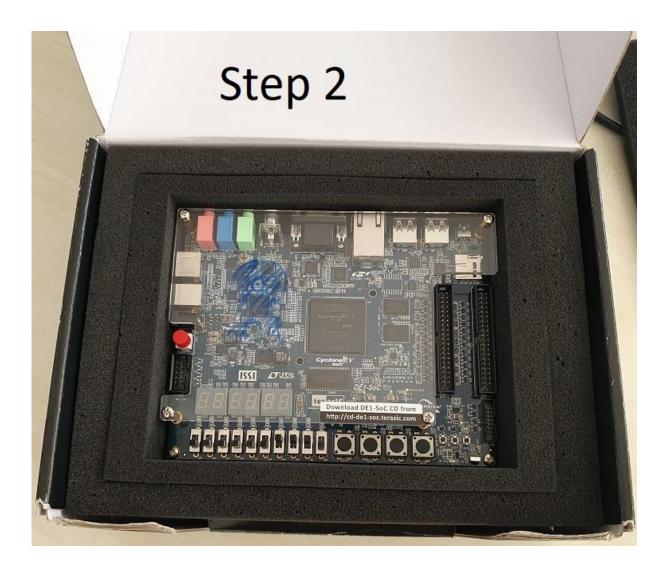

Figure 1-1 shows a photograph of the DE1-SoC package.

DE1-SoC User Manual

The DE1-SoC package includes:

- The DE1-SoC development board

- DE1-SoC Quick Start Guide

- USB cable (Type A to B) for FPGA programming and control

- USB cable (Type A to Mini-B) for UART control

- 12V DC power adapter

# 1.2 DE1-SoC System CD

The DE1-SoC System CD contains all the documents and supporting materials associated with DE1-SoC, including the user manual, system builder, reference designs, and device datasheets. Users can download this system CD from the link: <u>http://cd-de1-soc.terasic.com</u>.

# **1.3 Getting Help**

Here are the addresses where you can get help if you encounter any problems:

- Altera Corporation

- 101 Innovation Drive San Jose, California, 95134 USA

Email: <u>university@altera.com</u>

- Terasic Technologies

- 9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

Email: <a href="mailto:support@terasic.com">support@terasic.com</a>

Tel.: +886-3-575-0880

Website: <u>de1-soc.terasic.com</u>

# Chapter 2 Introduction of the DE1-SoC Board

This chapter provides an introduction to the features and design characteristics of the board.

# **2.1 Layout and Components**

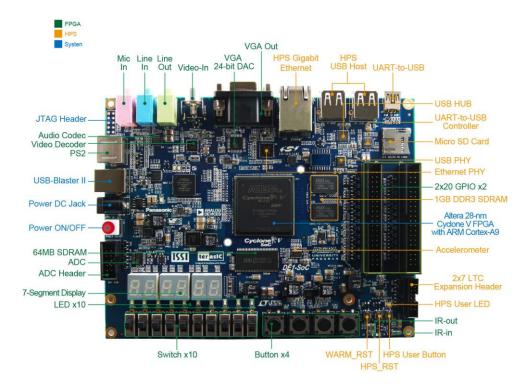

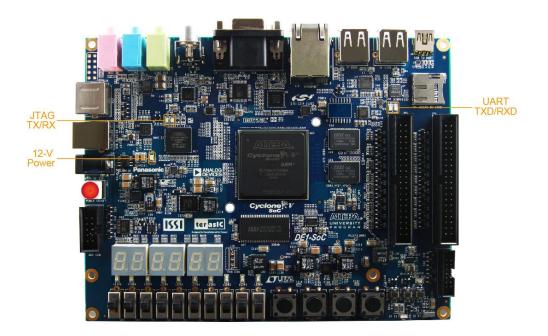

**Figure 2-1** shows a photograph of the board. It depicts the layout of the board and indicates the location of the connectors and key components.

Figure 2-1 DE1-SoC development board (top view)

Figure 2-2 De1-SoC development board (bottom view)

The DE1-SoC board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects.

DE1-SoC User Manual

The following hardware is provided on the board:

# ■ FPGA

- Altera Cyclone® V SE 5CSEMA5F31C6N device

- Altera serial configuration device EPCS128

- USB-Blaster II onboard for programming; JTAG Mode

- 64MB SDRAM (16-bit data bus)

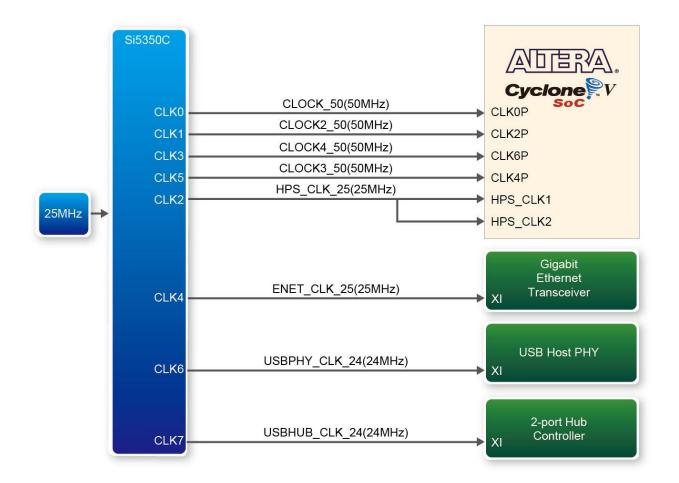

- 4 push-buttons

- 10 slide switches

- 10 red user LEDs

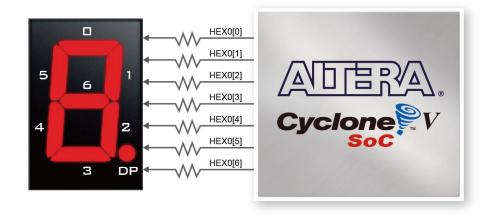

- Six 7-segment displays

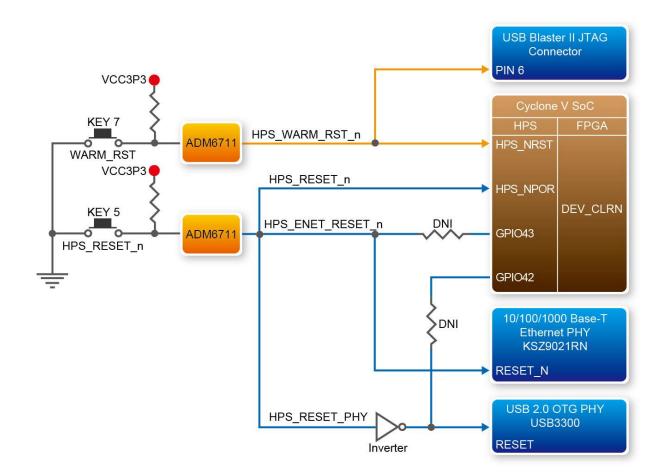

- Four 50MHz clock sources from the clock generator

- 24-bit CD-quality audio CODEC with line-in, line-out, and microphone-in jacks

- VGA DAC (8-bit high-speed triple DACs) with VGA-out connector

- TV decoder (NTSC/PAL/SECAM) and TV-in connector

- PS/2 mouse/keyboard connector

- IR receiver and IR emitter

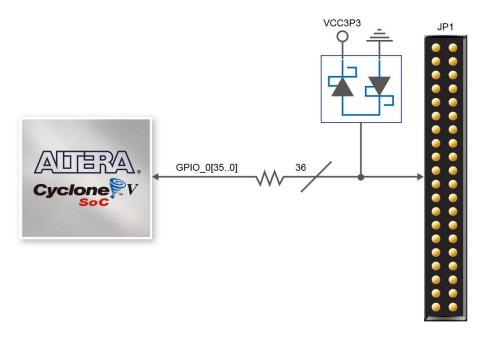

- Two 40-pin expansion header with diode protection

- A/D converter, 4-pin SPI interface with FPGA

- HPS (Hard Processor System)

- 800MHz Dual-core ARM Cortex-A9 MPCore processor

- 1GB DDR3 SDRAM (32-bit data bus)

- 1 Gigabit Ethernet PHY with RJ45 connector

- 2-port USB Host, normal Type-A USB connector

- Micro SD card socket

- Accelerometer (I2C interface + interrupt)

- UART to USB, USB Mini-B connector

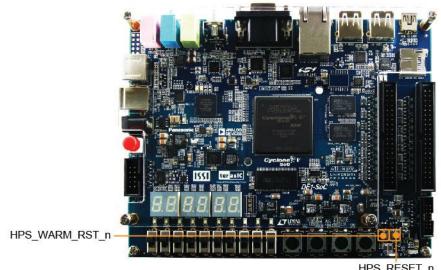

- Warm reset button and cold reset button

- One user button and one user LED

- LTC 2x7 expansion header

# 2.2 Block Diagram of the DE1-SoC Board

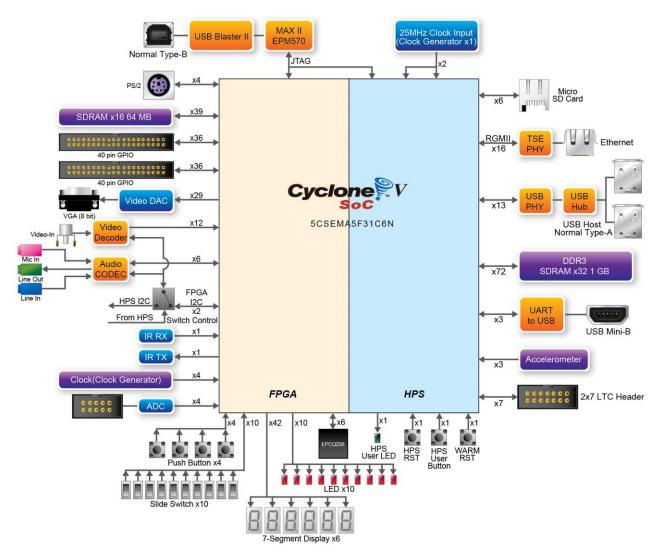

**Figure 2-3** is the block diagram of the board. All the connections are established through the Cyclone V SoC FPGA device to provide maximum flexibility for users. Users can configure the FPGA to implement any system design.

Figure 2-3 Block diagram of DE1-SoC

Detailed information about **Figure 2-3** are listed below.

# **FPGA Device**

- Cyclone V SoC 5CSEMA5F31 Device

- Dual-core ARM Cortex-A9 (HPS)

- 85K programmable logic elements

- 4,450 Kbits embedded memory

- 6 fractional PLLs

- 2 hard memory controllers

DE1-SoC User Manual

## **Configuration and Debug**

- Quad serial configuration device EPCS128 on FPGA

- Onboard USB-Blaster II (normal type B USB connector)

## **Memory Device**

- 64MB (32Mx16) SDRAM on FPGA

- 1GB (2x256Mx16) DDR3 SDRAM on HPS

- Micro SD card socket on HPS

#### Communication

- Two port USB 2.0 Host (ULPI interface with USB type A connector)

- UART to USB (USB Mini-B connector)

- 10/100/1000 Ethernet

- PS/2 mouse/keyboard

- IR emitter/receiver

- I2C multiplexer

#### Connectors

- Two 40-pin expansion headers

- One 10-pin ADC input header

- One LTC connector (one Serial Peripheral Interface (SPI) Master ,one I2C and one GPIO interface )

# Display

• 24-bit VGA DAC

#### Audio

• 24-bit CODEC, Line-in, Line-out, and microphone-in jacks

# Video Input

• TV decoder (NTSC/PAL/SECAM) and TV-in connector

# ADC

- Interface: SPI

- Fast throughput rate: 500 KSPS

- Channel number: 8

- Resolution: 12-bit

- Analog input range : 0 ~ 4.096

## Switches, Buttons, and Indicators

- 5 user Keys (FPGA x4, HPS x1)

- 10 user switches (FPGA x10)

- 11 user LEDs (FPGA x10, HPS x 1)

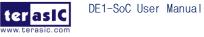

- 2 HPS reset buttons (HPS\_RESET\_n and HPS\_WARM\_RST\_n)

- Six 7-segment displays

#### Sensors

• G-Sensor on HPS

#### Power

• 12V DC input

# Chapter 3 Using the DE1-SoC Board

This chapter provides an instruction to use the board and describes the peripherals.

# **3.1 Settings of FPGA Configuration Mode**

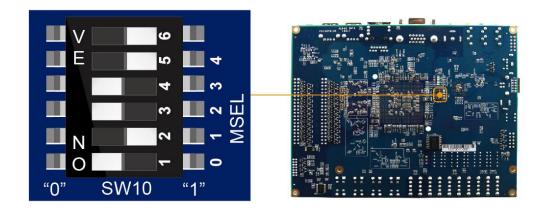

When the DE1-SoC board is powered on, the FPGA can be configured from EPCS or HPS. The MSEL[4:0] pins are used to select the configuration scheme. It is implemented as a 6-pin DIP switch **SW10** on the DE1-SoC board, as shown in **Figure 3-1**.

Figure 3-1 DIP switch (SW10) setting of Active Serial (AS) mode at the back of DE1-SoC board

Table 3-1 shows the relation between MSEL[4:0] and DIP switch (SW10).

| Board Reference | Signal Name | Description                                            | Default   |

|-----------------|-------------|--------------------------------------------------------|-----------|

| SW10.1          | MSEL0       |                                                        | ON ("0")  |

| SW10.2          | MSEL1       | Use these pins to set the FPGA<br>Configuration scheme | OFF ("1") |

| SW10.3          | MSEL2       |                                                        | ON ("0")  |

| SW10.4          | MSEL3       |                                                        | ON ("0")  |

| SW10.5          | MSEL4       |                                                        | OFF ("1") |

| SW10.6          | N/A         | N/A                                                    | N/A       |

| Table 3-1 FPGA | Configuration | Mode Switch  | (SW10) |

|----------------|---------------|--------------|--------|

|                | Comiguration  | mout by much |        |

Figure 3-1 shows MSEL[4:0] setting of AS mode, which is also the default setting on DE1-SoC. When the board is powered on, the FPGA is configured from EPCS, which is pre-programmed with the default code. If developers wish to reconfigure FPGA from an application software running on Linux, the MSEL[4:0] needs to be set to "01010" before the programming process begins. If developers using the "Linux Console with frame buffer" or "Linux LXDE Desktop" SD Card image, the MSEL[4:0] needs to be set to "00000" before the board is powered on.

| Table 3-2 MSEL Pin Settings for FPGA Configure of DE1-Soc |                  |                                                   |  |  |  |  |  |

|-----------------------------------------------------------|------------------|---------------------------------------------------|--|--|--|--|--|

| MSEL[4:0]                                                 | Configure Scheme | Description                                       |  |  |  |  |  |

| 10010                                                     | AS               | FPGA configured from EPCS (default)               |  |  |  |  |  |

| 01010                                                     | FPPx32           | FPGA configured from HPS software: Linux          |  |  |  |  |  |

|                                                           |                  | FPGA configured from HPS software: U-Boot, with   |  |  |  |  |  |

| 00000                                                     | FPPx16           | image stored on the SD card, like LXDE Desktop or |  |  |  |  |  |

|                                                           |                  | console Linux with frame buffer edition.          |  |  |  |  |  |

Table 2.2 MSEL Din Settings for EDCA Configure of DE1 SeC

# **3.2 Configuration of Cyclone V SoC FPGA on DE1-SoC**

There are two types of programming method supported by DE1-SoC:

1. JTAG programming: It is named after the IEEE standards Joint Test Action Group.

The configuration bit stream is downloaded directly into the Cyclone V SoC FPGA. The FPGA will retain its current status as long as the power keeps applying to the board; the configuration information will be lost when the power is off.

AS programming: The other programming method is Active Serial configuration. 2.

The configuration bit stream is downloaded into the quad serial configuration device (EPCS128), which provides non-volatile storage for the bit stream. The information is retained within EPCS128

even if the DE1-SoC board is turned off. When the board is powered on, the configuration data in the EPCS128 device is automatically loaded into the Cyclone V SoC FPGA.

#### ■ JTAG Chain on DE1-SoC Board

The FPGA device can be configured through JTAG interface on DE1-SoC board, but the JTAG chain must form a closed loop, which allows Quartus II programmer to the detect FPGA device. **Figure 3-2** illustrates the JTAG chain on DE1-SoC board.

Figure 3-2 Path of the JTAG chain

#### **Configure the FPGA in JTAG Mode**

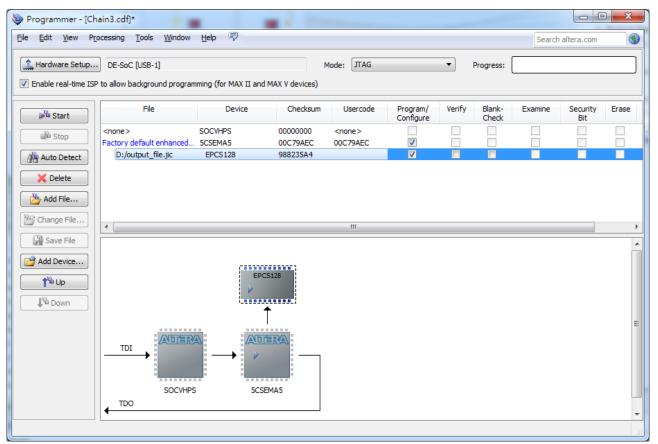

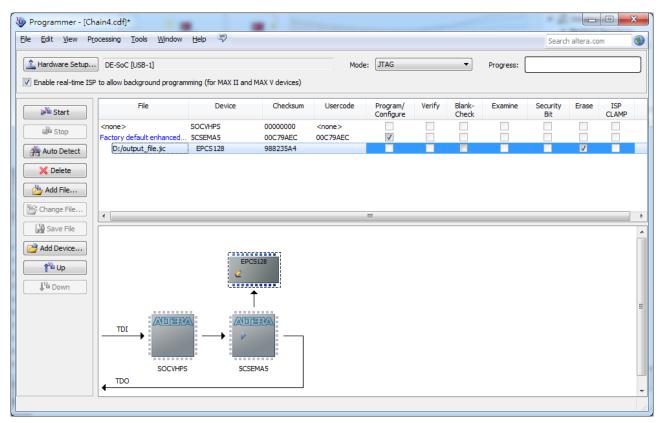

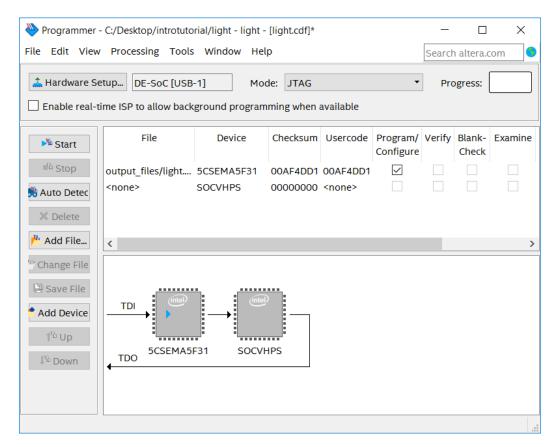

There are two devices (FPGA and HPS) on the JTAG chain. The following shows how the FPGA is programmed in JTAG mode step by step.

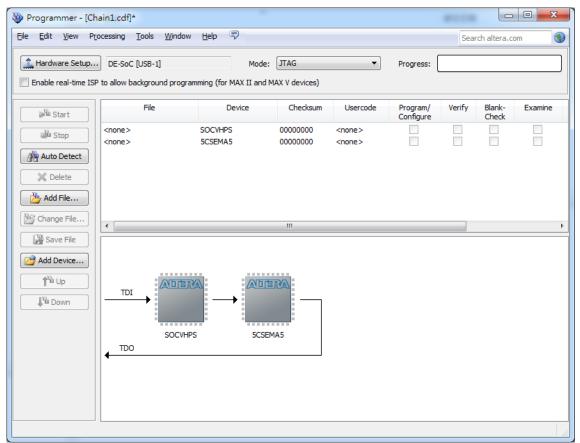

1. Open the Quartus II programmer and click "Auto Detect", as circled in Figure 3-3

| 🕲 Programmer - [Chain3.cdf]       |                                                   |                     |                |            |                       |        |                 |         |

|-----------------------------------|---------------------------------------------------|---------------------|----------------|------------|-----------------------|--------|-----------------|---------|

| <u>File E</u> dit <u>V</u> iew Pr | ocessing <u>T</u> ools <u>W</u> indow <u>H</u> el | lp 💎                |                |            |                       | Sear   | ch altera.co    | m 🕥     |

| Hardware Setup                    | DE-SoC [USB-1]                                    | Mode:               | JTAG           | <b>•</b> ] | Progress:             |        |                 |         |

| Enable real-time ISF              | P to allow background programming                 | I (for MAX II and M | IAX V devices) |            |                       |        |                 |         |

| Start                             | File                                              | Device              | Checksum       | Usercode   | Program/<br>Configure | Verify | Blank-<br>Check | Examine |

| Stop                              |                                                   |                     |                |            |                       |        |                 |         |

| Auto Detect                       |                                                   |                     |                |            |                       |        |                 |         |

| 🔀 Delete                          |                                                   |                     |                |            |                       |        |                 |         |

| Add File                          |                                                   |                     |                |            |                       |        |                 |         |

| Change File                       |                                                   |                     | III            |            |                       |        |                 | ۲       |

| Save File                         |                                                   |                     |                |            |                       |        |                 |         |

| Add Device                        |                                                   |                     |                |            |                       |        |                 |         |

|                                   |                                                   |                     |                |            |                       |        |                 |         |

| Down                              |                                                   |                     |                |            |                       |        |                 |         |

|                                   |                                                   |                     |                |            |                       |        |                 |         |

|                                   |                                                   |                     |                |            |                       |        |                 |         |

|                                   | 40.                                               |                     |                |            |                       |        |                 |         |

Figure 3-3 Detect FPGA device in JTAG mode

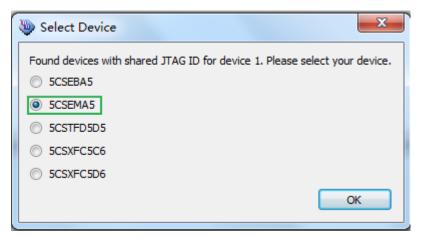

2. Select detected device associated with the board, as circled in Figure 3-4.

Figure 3-4 Select 5CSEMA5 device

3. Both FPGA and HPS are detected, as shown in Figure 3-5.

Figure 3-5 FPGA and HPS detected in Quartus programmer

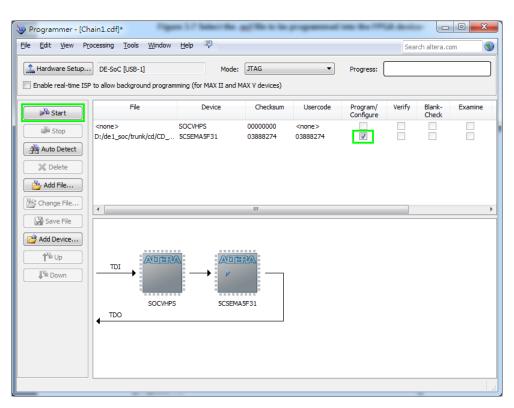

4. Right click on the FPGA device and open the .sof file to be programmed, as highlighted in **Figure 3-6**.

| y | Programmer - [Chain1.cdf]*                                      |                      |                   |          |              |                  |               |                       |        |                 |         |

|---|-----------------------------------------------------------------|----------------------|-------------------|----------|--------------|------------------|---------------|-----------------------|--------|-----------------|---------|

|   | File Edit View Processing Tools Window Help 💎 Search altera.com |                      |                   |          |              |                  |               |                       |        | om 🔇            |         |

|   | 🔔 Hardware Setup                                                | DE-SoC [USB-1]       |                   |          | Mode:        | JTAG             | •             | Progress:             |        |                 |         |

|   | Enable real-time ISF                                            | o to allow backgrour | d programming (fo | or MA    | X II and M   | AX V devices)    |               |                       |        |                 |         |

| Γ | Start                                                           | File                 |                   | Dev      | vice         | Checksum         | Usercode      | Program/<br>Configure | Verify | Blank-<br>Check | Examine |

|   | Stop                                                            | <none></none>        | SOCVH             | IPS      |              | 00000000         | <none></none> |                       |        |                 |         |

|   | une Stop                                                        | <none></none>        | 5CS=M             |          |              | 0000000          | 20000 X       |                       |        |                 |         |

|   | Auto Detect                                                     |                      | >                 | < r      | Delete       |                  | Del           |                       |        |                 |         |

|   |                                                                 |                      |                   | 5        | Select All   |                  | Ctrl+A        |                       |        |                 |         |

|   | 🗙 Delete                                                        |                      | 4                 |          | Add File     |                  |               |                       |        |                 |         |

|   | Add File                                                        |                      | 24                | -        | Change File  |                  |               |                       |        |                 |         |

|   |                                                                 |                      |                   | <u> </u> |              |                  |               |                       |        |                 |         |

|   | 쌸 Change File                                                   | •                    | lž                | 3 1      | Save File    |                  |               |                       |        |                 | Þ       |

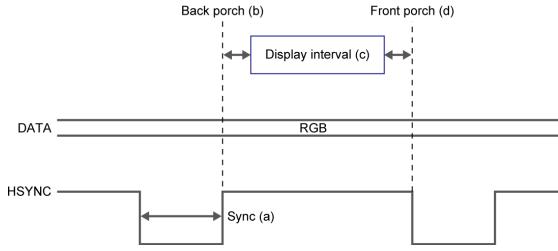

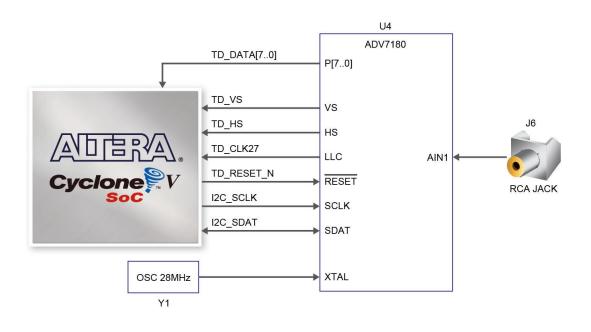

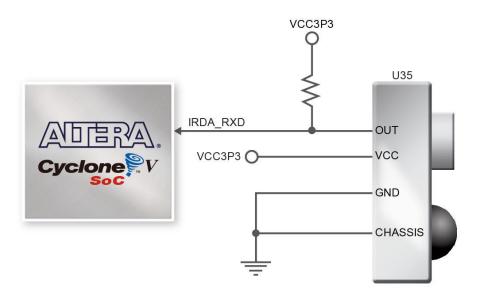

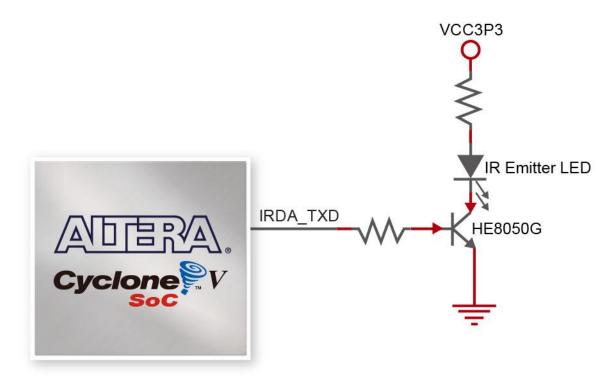

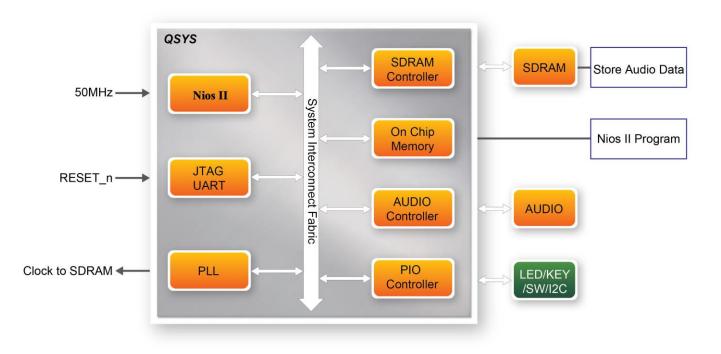

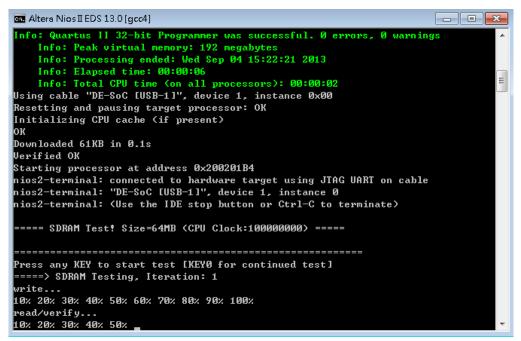

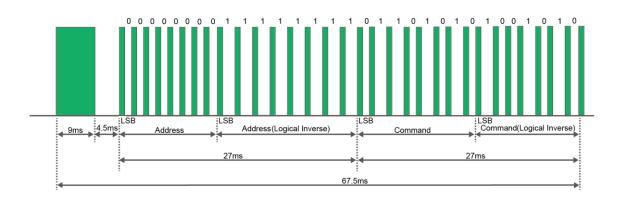

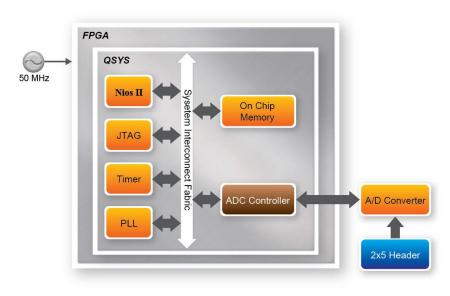

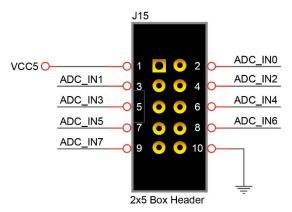

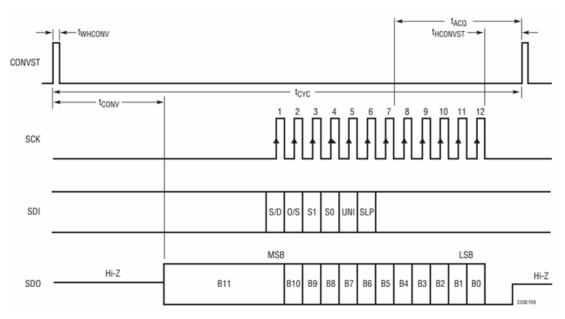

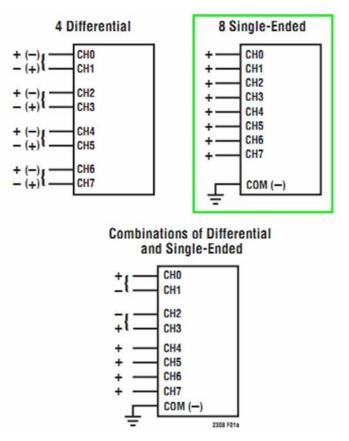

|   | Save File                                                       |                      |                   | ļ        | Add IPS File |                  |               |                       |        |                 |         |